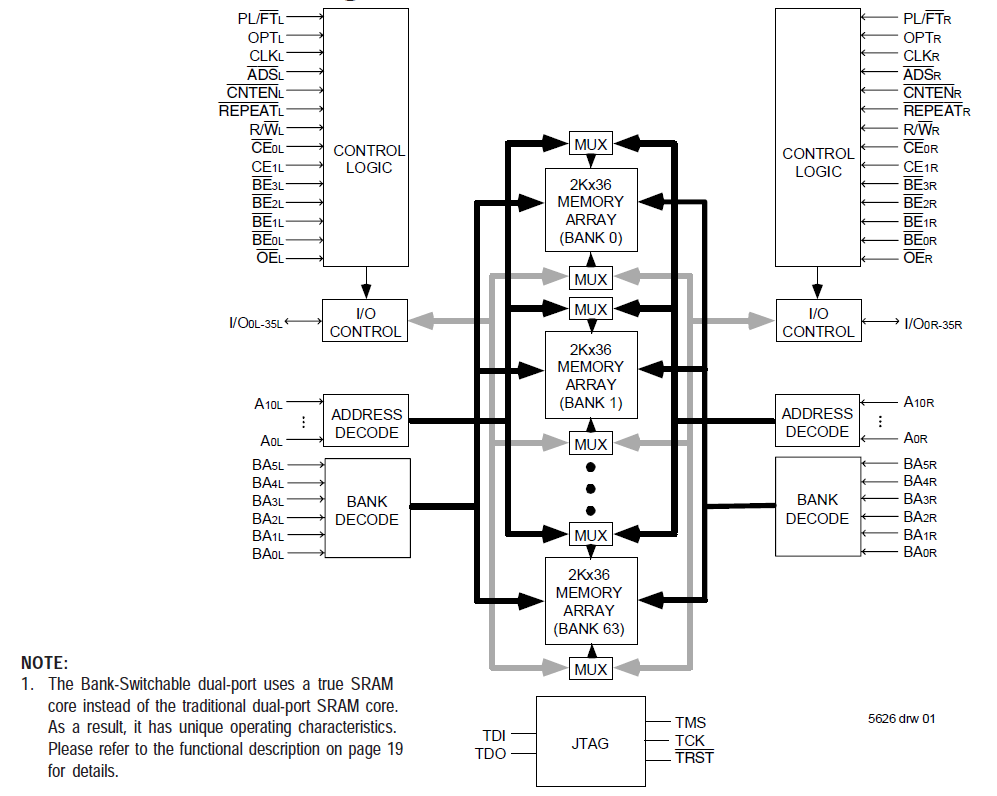

US8370557B2 - Pseudo dual-port SRAM and a shared memory switch using multiple memory banks and a sideband memory - Google Patents

![J11] A Charge-Domain Scalable-Weight In-Memory Computing Macro with Dual- SRAM Architecture for Precision-Scalable DNN Accelerators | SKKU IRIS Lab J11] A Charge-Domain Scalable-Weight In-Memory Computing Macro with Dual- SRAM Architecture for Precision-Scalable DNN Accelerators | SKKU IRIS Lab](https://iris.skku.edu/publication/j11_tcas1_2021/featured_hu6aef2193e6bece41bd2a0e680fa624e7_293978_720x2500_fit_q75_h2_lanczos.webp)

J11] A Charge-Domain Scalable-Weight In-Memory Computing Macro with Dual- SRAM Architecture for Precision-Scalable DNN Accelerators | SKKU IRIS Lab

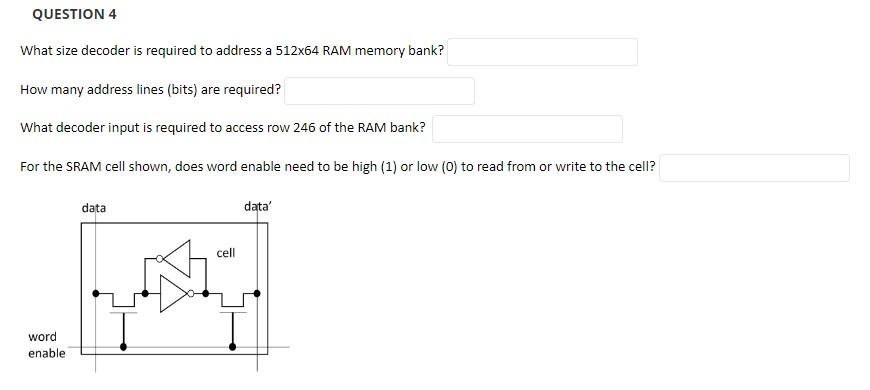

Multi-port SRAM with Multi-bank for Self-organizing Maps Neural Network (Invited paper) | Semantic Scholar

Multi-Port SRAM Overview. ® Slide 2 Objectives n What are Multi-Port SRAMs? n Why are they needed? n Arbitration Features l Busy l Interrupt l Semaphore. - ppt download

Multi-port SRAM with Multi-bank for Self-organizing Maps Neural Network (Invited paper) | Semantic Scholar

Figure 5 from A 0.6-Tbps, 16-port SRAM design with 2-stage- pipeline and multi-stage-sensing scheme | Semantic Scholar

a) Memory bank construction using single-port SRAMs and (b) proposed... | Download Scientific Diagram

Figure 18 from Single-Ended Subthreshold SRAM With Asymmetrical Write/Read-Assist | Semantic Scholar